DDR4時代的來臨(2)?

繼續DDR4上網介紹

方法/步驟

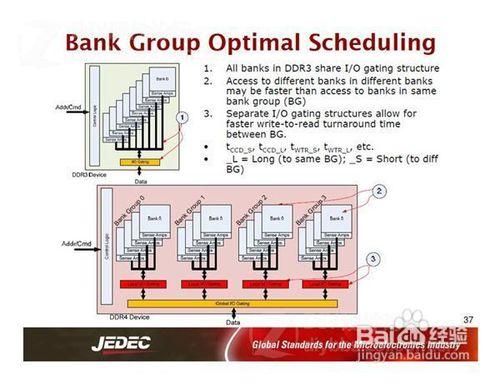

Bank分組優化調度:DDR3裡的所有Bank都是共享I/O柵極結構的,DDR4則進行了分組,不同分組之間的寫入-讀取轉換速度會更快。

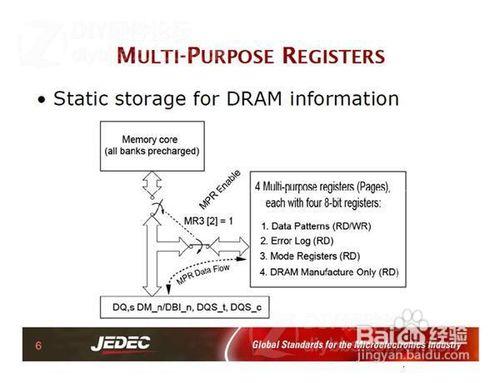

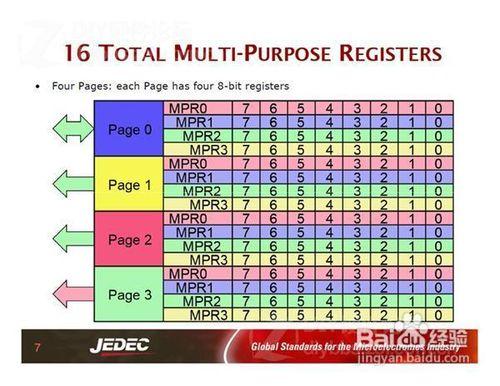

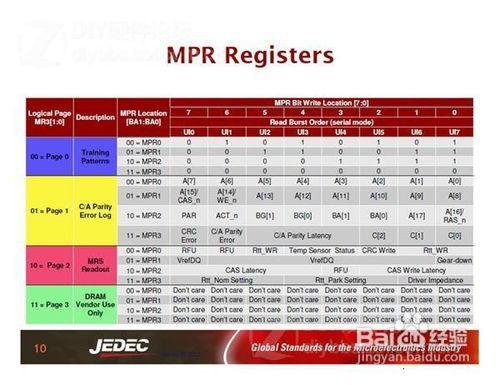

多重目的寄存器:四個頁面(Pages),每頁有四個8-bit寄存器,總共16個。

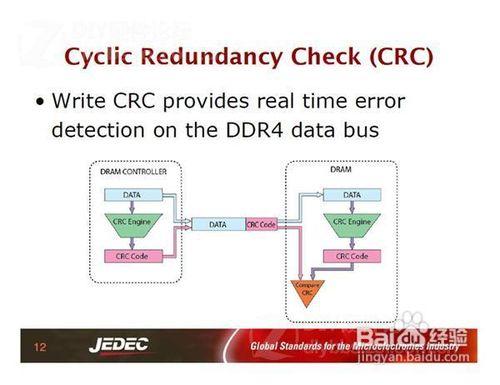

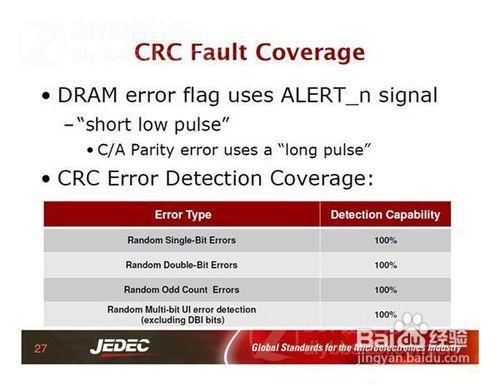

循環冗餘校驗(CRC):寫入CRC可以在DDR4數據總線上提供實時的錯誤檢測,對於四種隨機錯誤的檢測率可達100%。

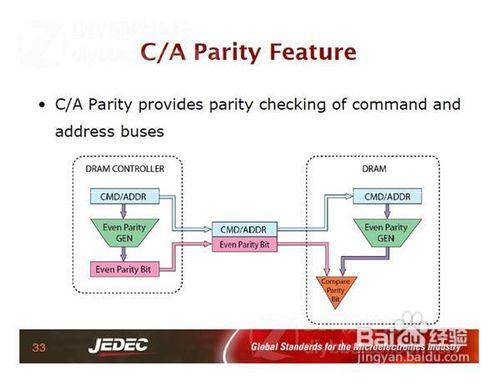

C/A對等功能可以檢查命令與地址總線。

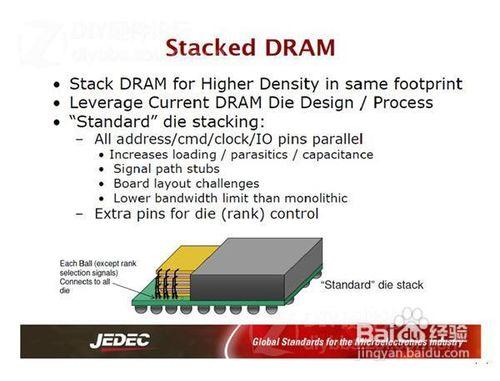

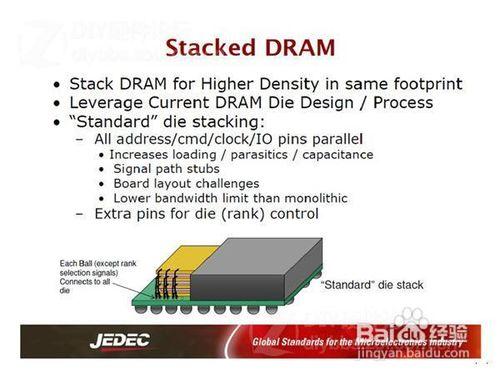

Die堆疊是實現DDR4更高存儲密度的關鍵,當然這樣對製造工藝、電路佈局、信號傳輸、指令控制等都提出了更苛刻的要求,當然成本也會高不少。這種新的內存封裝方式被稱為“3DS”(不是任天堂掌機)

製造技術上主要是流行的硅穿孔(TSV),其它垂直電氣連接技術也可以。每個Ball都與所有的Die相連。

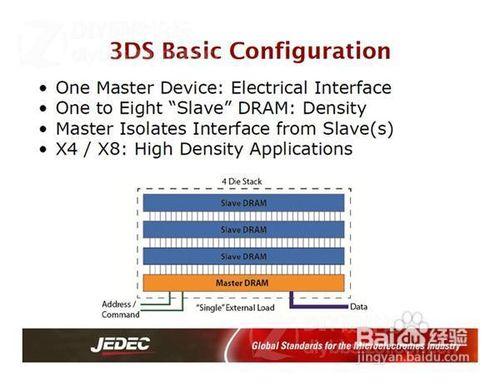

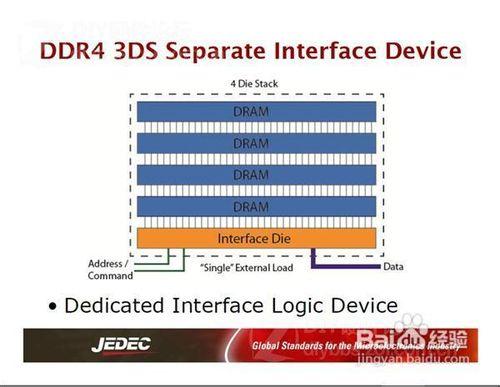

內部Die配置上採用了主從區分的方式,其中主Die一個、從Die一至八個。只有主Die可以對外聯繫,其它Die都隱藏在幕後

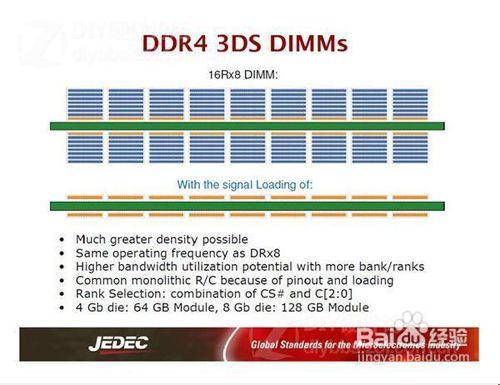

這種設計帶來了更高的存儲密度和帶寬利用率,同時又保持了信號傳輸等方面的一致性和兼容性。如果使用4Gb(512MB)的Die,單條內存最大容量可達64GB,8Gb Die就可以實現128GB