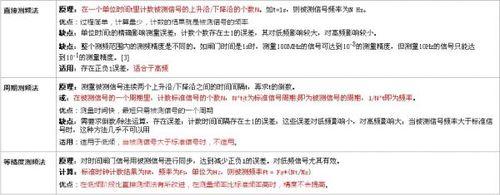

常用的測頻方法

① 利用電路的某種頻率響應特性來測量頻率,如諧振測頻法[低頻測量,應用較廣]、電橋測頻法[高頻、微波段測量]

② 利用標準頻率與測頻進行比較來測量,精度取決於標準頻率的準確度,如拍頻法[低頻]、示波器法[低頻]、差頻法[高頻]

③ 電子計數測頻法[適用於用數位電路實現]:直接測頻法[測週期法和測頻率法]和等精度測頻法

工具/語言

工具:Quartus

語言:VerilogHDL

原理

頻率測量的常用方法

等精度測頻法原理

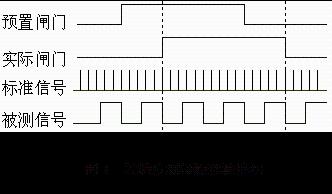

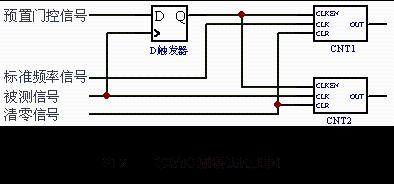

等精度測頻方法是在直接測頻方法的基礎上發展起來的。如圖1所示,它的閘門時間不是固定的值,而是被測訊號週期的整數倍,即與被測訊號同步,其實現方式可用圖2來說明。圖中,預置門控訊號是為Tpr 的一個脈衝,CNT1和CNT2是兩個可控計數器。標準頻率訊號從CNT1的時鐘輸入端CLK輸入,其頻率為fs 。經整形後的被測訊號(頻率為fx)從CNT2的時鐘輸入端CLK輸入,當預置門訊號為高電平(預置時間開始)時,被測訊號的上升沿通過D觸發器的Q端同時啟動計數器CNT1和CNT2計數。CNT1和CNT2分別對被測訊號(頻率為fx)和標準頻率訊號(頻率為fs)同時記數。同樣,當預置門訊號為低電平(預置時間結束)時,隨後而至的被測訊號的上升沿通過D觸發器的輸出端,同時關閉計數器的計數。設在一次預置門時間Tpr中計數器對被測訊號的計數值為Nx,對標準訊號的計數值為Ns。則下式成立:

由此可推得:

等精度測頻法具有三個特點:

(1)相對測量誤差與被測頻率的高低無關;

(2)增大Tpr或fs可以增大Ns,減少測量誤差,提高測量精度;

(3)測量精度與預置門和標準頻率有關,與被測訊號的頻率無關,在預置門和常規測頻閘門時間相同而被測訊號頻率不同的情況下,等精度測量法的測量精度不變。

一種實現過程

① 預設閘門模組:由標準時鍾產生預設閘門訊號。如標準時鍾100us[10kHz],計數1000次,產生預設閘門訊號為100ms

② 實際閘門模組:用被測訊號來同步預設閘門模組產生的閘門訊號來產生新的實際閘門訊號,本質是一個D觸發器

③ 計數模組:在實際閘門訊號有效時,標準時鍾和被測訊號同時計數,在閘門訊號結束時輸出計數結果

④ 頻率計算模組:由公式進行乘法和除法運算

直接計數測頻法

測頻法原理:在確定的閘門時間Tw內,記錄被測訊號的變化週期數或脈衝個數Nx,有fx=Nx/Tw

測週期法原理:需要有標準訊號頻率fs,在待測訊號的一個週期時間Tx內,記錄標準頻率的週期數Ns,有fx=fs/Ns

最高測量頻率為標準訊號頻率。

測量誤差:兩種方法都會產生±1個字的誤差。最大誤差為1/N,N為週期個數。

直接計數測頻法缺點:整個測頻範圍內的測頻精度是不同的。如閘門時間是1s時,測量100MHz的訊號可達到10-8的測量精度,但測量10Hz的訊號只能達到10-1的測量精度。

參考訊號:測頻法需要得到一個標準的脈寬,測週期法需要一個標準時鍾。實際上標準的脈寬必須從一個標準時鍾分頻得到,而一般,標準始終是從外部晶振分頻得到。

測量時間:當計數週期為106個時,計數時間為1s

實現方法

除法運算的Verilog實現(累加比較法)

module mydiv(clk, dataa, datab, start, datac);

input clk;

input [7:0] dataa;//被除數

input [7:0] datab;//除數

input start;//開始新的運算

output [7:0] datac;//商

reg [7:0] datac;

reg [7:0] cbuf;

reg [7:0] temp;

always @(posedge clk)

begin

if(1'b1 == start)

begin

temp <= 8'd0;

cbuf <= 8'd0;

end

else if (dataa > temp)

begin

temp <= temp + datab;

cbuf <= cbuf + 8'h01;

end

else

begin

datac <= cbuf;

end

end

Endmodule

直接測頻法

閘門產生模組/gateout輸出1s,clk設為1ms

module gate(clk, gateout);

input clk;

output gateout;

reg [9:0] cnt;

reg gatebuf;

assign gateout = gatebuf;

always @(posedge clk)

begin

if (10'd999 == cnt)

begin

cnt <= 10'd0;

gatebuf <= ~gatebuf; //產生1s閘門

end

else

begin

cnt <= cnt + 10'd1;

end

end

endmodule

計數模組

說明:閘門訊號高有效下進行計數,當閘門訊號為低時停止計數並輸出計數結果。採用5位十進位制計數

module cnt(clk, gate, done, dtwo, dthree, dfour, dfive);

input clk;

input gate;

output done;//個位

output dtwo;//十位

output dthree;//百位

output dfour;//千位

output dfive;//萬位

reg [3:0] done, dtwo, dthree, dfour, dfive;

reg [3:0] ddone, ddtwo, ddthree, ddfour, ddfive;

reg gatebuf;

always @(posedge clk)

begin

gatebuf <= gate;

end

always @(posedge clk)

begin

if((gatebuf == 1'b0) && (gate == 1'b1))

begin

ddone <= 4'd1;

ddtwo <= 4'd0;

ddthree <= 4'd0;

ddfour <= 4'd0;

ddfive <= 4'd0;

end

else if((gatebuf == 1'b1) && (gate == 1'b0))

begin

done <= ddone;

dtwo <= ddtwo;

dthree <= ddthree;

dfour <= ddfour;

dfive <= ddfive;

end

else if(gate == 1'b1)

begin

if (ddone == 4'd9)

begin

ddone <= 4'd0;

if (ddtwo == 4'd9)

begin

ddtwo <= 4'd0;

if (ddthree == 4'd9)

begin

ddthree <= 4'd0;

if (ddfour == 4'd9)

begin

ddfour <= 4'd0;

if (ddfive == 4'd9)

begin

ddfive <= 0;

end

else

begin

ddfive <= ddfive + 4'd1;

end

end

else

begin

ddfour <= ddfour + 4'd1;

end

end

else

begin

ddthree <= ddthree + 4'd1;

end

end

else

begin

ddtwo <= ddtwo + 4'd1;

end

end

else

begin

ddone <= ddone + 4'd1;

end

end

end

endmodule

週期測頻法

計數模組

module periodcnt(clk, clkt, cntout,cntok);

input clk;//標準時鍾訊號

input clkt;//被測訊號

output [19:0] cntout;//計數結果輸出

output cntok;//計數結果輸出標誌

reg [19:0] cntout, cnt;

reg cntok, clktbuf;

always @(posedge clk)

begin

clktbuf <= clkt;

end

always @(posedge clk)

begin

if((clkt == 1'b1) && (clktbuf == 1'b0))//在被測訊號上升沿輸出計數結果並置計數為1

begin

cntout <= cnt;

cnt <= 20'd1;

cntok <= 1'b1;

end

else

begin

cnt <= cnt + 20'd1;

cntok <= 1'b0;

end

end

endmodule

除法運算模組

module perioddiv(clk, datab, start, datac);

input clk;

input [19:0] datab;

input start;

output [19:0] datac;

reg [19:0] dataa,datac, databbuf;

reg [19:0] cbuf;

reg [19:0] temp;

reg finish, cntflag;

always @(posedge clk)

begin

if((1'b1 == start) && (finish == 1'b0) && (datab != 20'd0))

begin

dataa <= 1000000;

temp <= datab;

cbuf <= 20'd1;

databbuf <= datab;

cntflag <= 1'b1;

end

else if ((dataa > temp) && (cntflag == 1'b1) )

begin

temp <= temp + databbuf;

cbuf <= cbuf + 20'd1;

finish <= 1'b1;

end

else

begin

datac <= cbuf;

finish <= 1'b0;

cntflag <= 1'b0;

end

end

endmodule

等精度測頻法

預設閘門模組:由標準時鍾計數產生

module pregate(clk, gateout);

input clk;

output gateout;

reg gateout, gatebuf;

reg [19:0] cnt;

always @(posedge clk)

begin

if (cnt == 20'd1000)

begin

gatebuf <= ~gatebuf;

gateout <= gatebuf;

cnt <= 20'd0;

end

else

begin

cnt <= cnt + 20'd1;

end

end

endmodule

實際閘門模組:由被測訊號來同步預設閘門模組產生

module actgate(clk, gatein, gateout);

input clk;

input gatein;

output gateout;

reg gateout;

always @(posedge clk)

begin

gateout <= gatein;

end

endmodule

計數模組:在實際閘門訊號有效時,標準時鍾與被測訊號同時進行計數;在閘門訊號結束時輸出計數結果

module cnt(clk, gate, cntout);

input clk;

input gate;

output [19:0] cntout ;

reg [19:0] cnt, cntout;

reg gatebuf;

always @(posedge clk)

begin

gatebuf <= gate;

end

always @(posedge clk)

begin

if((gate == 1'b1) && (gatebuf == 1'b0))

begin

cnt <= 20'd1;

end

else if((gate == 1'b0) && (gatebuf == 1'b1))

begin

cntout <= cnt;

end

else if(gatebuf == 1'b1)

begin

cnt <= cnt + 20'd1;

end

end

endmodule

頻率計數模組:根據公式計算

module frediv(clk, datat,datas, freout);

input clk;

input [19:0] datat;

input [19:0] datas;

output [19:0] freout;

reg [19:0] datam,freout, databbuf;

reg [19:0] cbuf;

reg [19:0] temp;

reg finish, cntflag;

always @(posedge clk)

begin

if((finish == 1'b0) && (datas != 20'd0) && (datat != 20'd0))

begin

datam <= 20'd10000 * datat;

temp <= datas;

cbuf <= 20'd1;

databbuf <= datas;

cntflag <= 1'b1;

finish <= 1'b1;

end

else if ((datam > temp) && (cntflag == 1'b1) )

begin

temp <= temp + databbuf;

cbuf <= cbuf + 20'd1;

end

else

begin

freout <= cbuf;

finish <= 1'b0;

cntflag <= 1'b0;

end

end

endmodule