許多應用都採用隔離式半橋柵極驅動器來控制大量功率,從要求高功率密度和效率的隔離式DC-DC電源模塊,到高隔離電壓和長期可靠性至關重要的太陽能逆變器等等,不一而足。下面將詳細闡述這些設計理念,以展現採用小型封裝的隔離式半橋柵極驅動器IC的卓越能力。

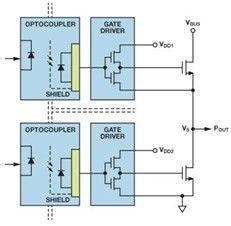

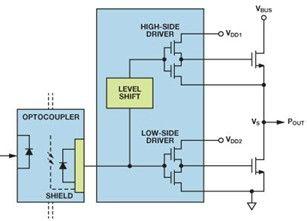

採用光耦合器隔離的基本半橋驅動器(如圖1所示)以極性相反的信號來驅動高端和低端N溝道MOSFET(或IGBT)的柵極,由此來控制輸出功率。驅動器必須具備低輸出阻抗以減少傳導損耗,同時還須具有快速開關能力以減少開關損耗。出於精度和效率的考慮,高端和低端驅動器需要具備高度匹配的時序特性,以便減少在半橋的第一個開關關閉,第二個開關開啟前的停滯時間。

圖1. 高壓半橋柵極驅動器

如圖所示,這種功能的一種常規實現方式是用一個光耦合器進行隔離,其後用一個高壓柵極驅動器IC.這種電路的一個潛在不足,就是單隔離輸入通道依賴高壓驅動器電路來實現所需要的通道間時序匹配和停滯時間。另一問題是,高壓柵極驅動器並無電流隔離,而是依賴IC的結隔離來分離高端驅動電壓和低端驅動電壓。在低端開關事件中,電路中的寄生電感可能導致輸出電壓VS降至地電壓以下。發生這種情況時,高端驅動器可能發生閂鎖,並永久性損壞。

設計途徑

光耦合器柵極驅動器

另一種方法(如圖所示)利用兩個光耦合器和兩個柵極驅動器來實現輸出之間的電流隔離,從而避免了高端-低端交互作用的問題。柵極驅動器電路往往置於與光耦合器相同的封裝中,因而一般需要兩個獨立的光耦合器柵極驅動器IC來構成完整的隔離式半橋,結果使解決方案的物理尺寸變大。另需注意的是,兩個光耦合器即使封裝在一起,也是是獨立製造的,從而限制了匹配兩個通道的能力。這種失配會增加關閉一個通道與打開另一個通道之間的停滯時間,從而導致效率下降。

下圖 雙光耦合器半橋柵極驅動器

光耦合器的響應速度受到原邊發光二極管(LED)電容的限制,而且將輸出驅動至高達1 MHz的速度也會受到其傳播延遲(最大值為500 ns)以及較慢的上升和下降時間(最大值為100 ns)的限制。要使光耦合器接近最高速度,需要將LED電流增加至10 mA以上,這會消耗更多功率,縮短光耦合器的壽命並降低其可靠性,尤其是在太陽能逆變器和電源應用中常見的高溫環境下。

脈衝變壓器柵極驅動器

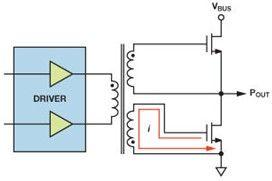

接下來,我們來看看通過變壓器耦合實現電流隔離的電路。這些電路的傳播延遲較低、時序特性更精確,與光耦合器相比,具有速度優勢。在圖3中,採用的是一個脈衝變壓器,其工作速度可以達到半橋柵極驅動器應用通常所需的水平(最高1 MHz)。柵極驅動器IC可用於提供容性MOSFET柵極充電所需的高電流。在此,柵極驅動器以差分方式驅動脈衝變壓器的原邊,兩個副邊繞組驅動半橋的各個柵極。在這種應用中,脈衝變壓器具有顯著優勢,不需要用隔離式電源來驅動副邊MOSFET.

如下圖. 脈衝變壓器半橋柵極驅動器

然而,當感應線圈中流動的較大瞬態柵極驅動電流導致振鈴時,就可能出現問題。結果可能使柵極不合需要地開啟和關閉,從而損壞MOSFET.脈衝變壓器的另一個侷限在於,它們在要求信號佔空比在50%以上的應用中可能表現欠佳。這是由於脈衝變壓器只能提供交流信號,而且鐵芯磁通量必須每半個週期復位一次以維持伏秒平衡。最後一點不足:脈衝變壓器的磁芯和隔離式繞組需要相對較大的封裝,再加上驅動器IC和其他分立式元件,最終形成的解決方案可能尺寸過大,無法適應許多高密度應用。

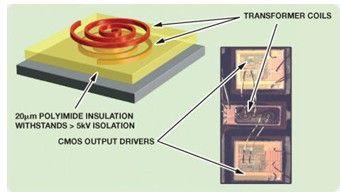

數字隔離器柵極驅動器

現在,我們來看看把數字隔離器用在隔離式半橋柵極驅動器中的情況。圖4中的數字隔離器使用標準CMOS集成電路工藝,以金屬層形成變壓器線圈,並以聚酰亞胺絕緣材料來分離線圈。這種組合可以實現5 kV rms以上(1分鐘額定值)的隔離能力,可用於魯棒型隔離電源和逆變器應用。

如下圖. 採用變壓器隔離的數字隔離器

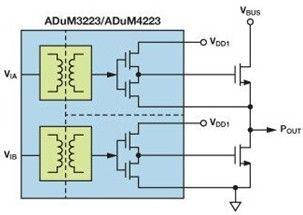

如圖所示,數字隔離器消除了光耦合器中使用的LED以及與之相關的老化問題,而且功耗更低、可靠性更高。輸入與輸出以及輸出與輸出之間提供電流隔離(虛線),以消除高端-低端的交互作用。輸出驅動器通過低輸出阻抗降低導通損耗,同時通過快速開關時間降低開關損耗。

如下圖. 採用數字隔離的4 A柵極驅動器

與光耦合器設計不同,高端和低端數字隔離器以單個集成電路為基礎製造而成,其輸出天生匹配,具有更高的效率。請注意,圖1所示高壓柵極驅動器集成電路會增加電平轉換電路中的傳播延遲,因而不能像數字隔離器一樣實現通道間時序特性的匹配。另外,在單個IC封裝中同時集成柵極驅動器和隔離機制可以最大限度地減小解決方案的尺寸。