對於廣大PCB設計工程師而言,提到時序問題,覺得比較茫然,看到時序圖,更是一頭霧水,感覺時序問題很高深。大家平常的設計中,最常見的是各種等長關係,網上流傳的Layout Guide,也會告訴大家那些線需要等長。是不是做到了等長,就滿足時序關係了呢?你有沒有想過,在有些情況下,費盡心思做的等長,反而是系統不工作,時序問題出錯的罪魁禍首呢?

筆者在給一些公司做時序培訓的時候,開場白一般會問一個問題:大家列舉下平常設計中的常見等長要求,一些具有共性的回答如下:

PCI總線,CPCI總線,PCIX數據地址總線:1000mil等長,有些回答甚至500mil或者更小。

SDRAM的數據地址總線,這時候有兩種回答:

1.全部總線等長,等長要求200mil以內(數值的回答不關鍵,隨著頻率等因素數值也經常變化,以下的討論相同,我們不關心具體要求是多長以內,而是等長的類型)

2.分組等長,D0~D7 ……,如果我再問分組和什麼Strobe做等長,答案更是千奇百怪(這個答案是被DDR影響了?新的工程師已經很少機會接觸SDRAM了)

DDR1、2、3

1.數據線分組等長,DQ0~7+DQS 數據組內20mil等長

2.地址、控制、命令和CLK等長,範圍稍微寬一些,+-500mil左右

3.所有DQS和CLK等長,甚至DDR3,做了Fly by設計之後,繼續要求等長關係

PCIE差分組內等長5mil以內

PCIE差分組間等長100mil(或者500mil)以內

經驗

大家可以先思考一下,上面這些等長關係,應該工作中都有可能碰到,你是不是也這麼做的,有沒有更深入思考過,哪些等長關係是不合理的?希望在時序的系列交流結束之後,大家能有更加明確的答案。

可以這麼說,絕大部分等長設計,都有相對應的時序關係,如果能看懂相關的時序圖,對等長設計會更加清晰。上面列舉等長要求的時候,其實做了分類,相對於高速總線的發展歷史,其實就是3個大類,共同時鐘的並行總線,源同步時鐘的並行總線,高速串行總線,如下圖所示:

我們討論下綠色的部分,也就是共同時鐘的並行總線時序設計。或許有人會說,這都是過時的設計了,並且200M以內的信號,有什麼好討論的?隨便設計就好了。其實現在很多系統還會採用CPCI的構架,PCIX的總線還在通訊、工控等行業大量採用。並且共同時鐘系統,到了133M以上,時序設計非常困難,可以說如果沒有真正理解時序設計的原理,你可能做一個5G的PCIE2.0的系統沒有什麼問題,做一個166M的PCIX系統,做一個失敗一個,系統完全無法運行在你預期的頻率上,不得不降頻使用。當然,這裡面有兩個原因,其一是每一代總線,發展到瓶頸之後才會進入下一代總線,在各自的瓶頸上,時序裕量非常小,設計極為困難。其二,由於技術的發展,大家更多的關注DDR3,關注高速串行總線,共同時鐘系統的研究越來越少,相應的總結文章也不常見,就帶來很多設計問題,也就是上面的回答裡面,SDRAM分組等長設計錯誤的原因。

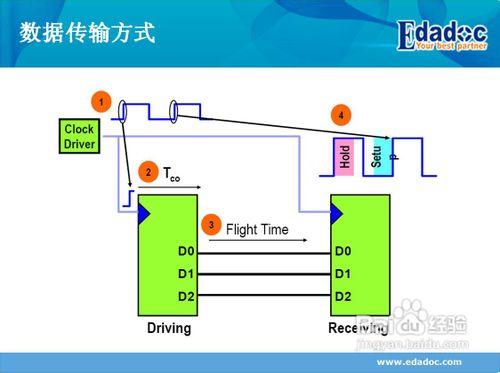

首先,我們怎麼判斷一個系統是共同時鐘,方法很簡單,找時鐘樹,確定時鐘的關係,是判斷各種時序系統的關鍵。共同時鐘系統,一般有一個外部的晶振或者晶體,然後通過時鐘分配器分別連到系統的驅動端和接收端,由這個外部時鐘線來控制系統的時序工作方式,如下圖所示:

第一個時鐘邊沿驅動端發數據,第二個時鐘邊沿,在接收端接收數據,為了保證數據的穩定可靠傳輸,需要滿足一定的建立保持時間裕量。

限於篇幅和時間關係,在這個小節先直接給出結論,下一個專題在針對結論具體討論,也留給大家思考的時間。

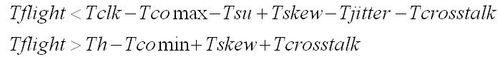

共同時鐘的時序關係公式為:

這兩個公式大家可以在各種文章裡面看到,從公式可以直接得出結論,共同時鐘的時序等長關係是一個範圍,而不是等長。又因為飛行時間的最小時序要求一般都可以滿足,也就是第二個公式在很多場合可以忽略不計,帶給PCB設計的要求就是符合第一個公式,結論就是走線越短越好。任何因為並不存在時序要求而做的整個總線繞等長,而又為了繞等長而導致這個總線的佈線度增加,串擾增加,這樣的設計是錯誤的,失敗的例子非常多。