在Verilog語言中,狀態機是最常用也是最重要的模塊,一個狀態機是否穩定,決定了整個電路工作的時鐘高低以及程序執行的正確性。

工具/原料

ISE 14.6

方法/步驟

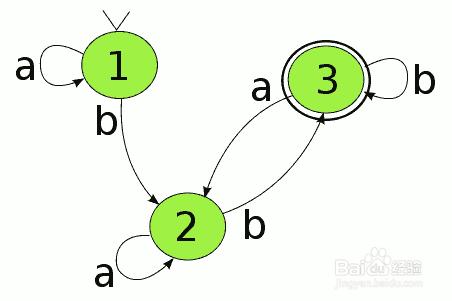

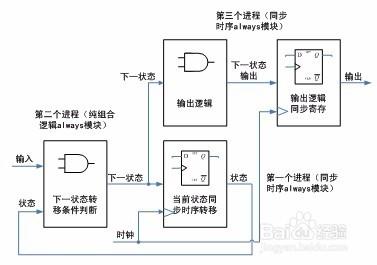

狀態機描述主要有以下幾個方面,即如何進行狀態轉移,狀態轉移的條件,每個狀態的輸出是什麼;而最佳的狀態機就是將三者分開,由組合邏輯和非組合邏輯搭配組成,這樣程序易讀,易維護,同時方便添加約束條件。

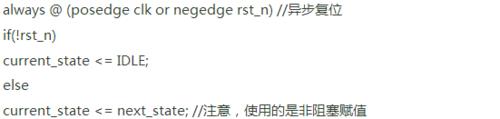

第一段狀態,時序電路的always模塊,用同步電路描述狀態跳轉的過程,這樣可利用觸發器消除不穩定狀態。

第二段狀態,組合邏輯always模塊,用以描述狀態轉移的判斷條件,利用組合邏輯實現,達到立即判斷的效果,在下一時鐘邊沿同步變化

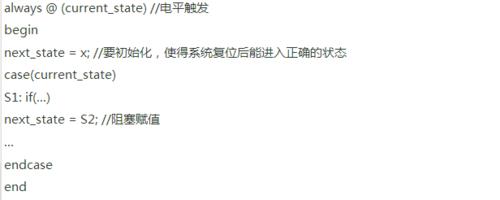

第三段狀態,時序電路always模塊,用以描述每一段狀態的結果輸出,使用時序電路實現,消除不穩定狀態的變化,達到同步跳轉的效果

三段式狀態機做到了同步寄存器輸出,消除了組合邏輯輸出的不穩定與毛刺的隱患,而且更利於時序路徑分組,在FPGA的綜合與佈局佈線效果更佳,提高電路運行時鐘,加大布線成功率。

注意事項

注意case語句都應加入defalut語句,以免綜合產生鎖存器