PLL,即鎖相環,是FPGA中的重要資源,因為一個複雜的FPGA系統往往需要多個不同的頻率、相位的時鐘訊號,所以PLL的正確配置對於FPGA來說至關重要。

工具/原料

電腦一臺

ISE14.4版本軟體

方法/步驟

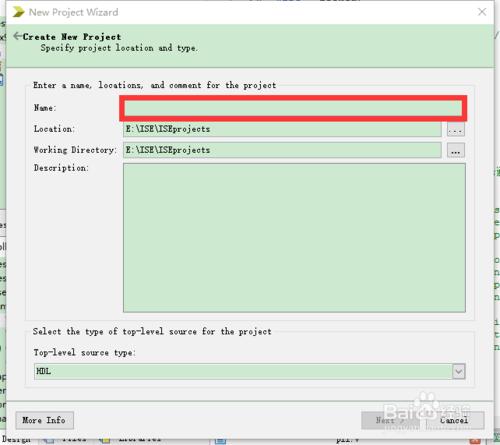

首先,在ISE14.4中新建一個工程。

點選New project...後,會出現create a new project對話方塊,在標紅的方框內起個名字,英文。

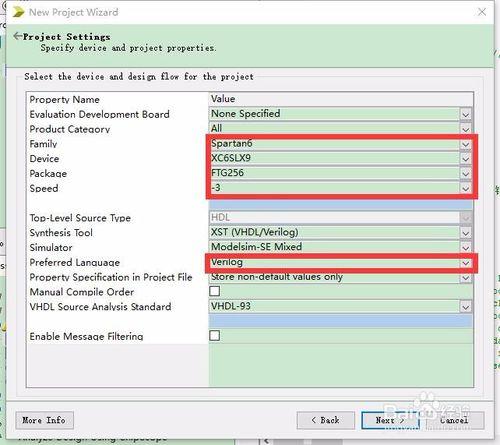

起好名字後,點選next。然後出現如下對話方塊,根據晶片手冊,將標紅的部分,設定正確,點選next.

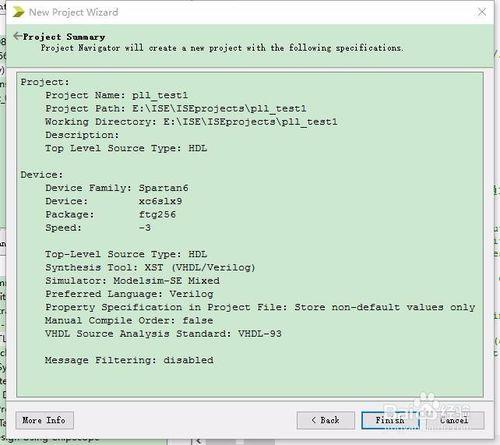

出現如下對話方塊,不用修改,點選finish。

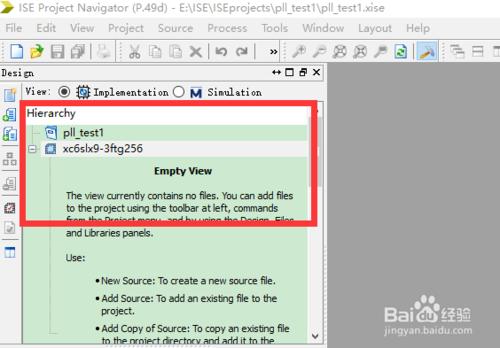

在左上角Hierarchy 方框內,如下圖所示。

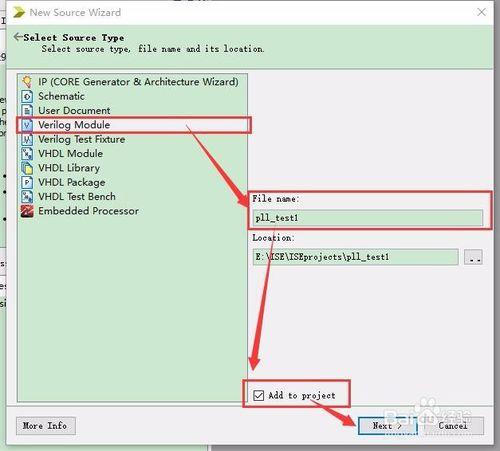

在上圖方框內,右擊,選擇New Source,出現如下對話方塊。先點選Verilog

Module, 再起個名字,再將add to project 勾選上,按照圖片內箭頭一步步進行。然後點選next。

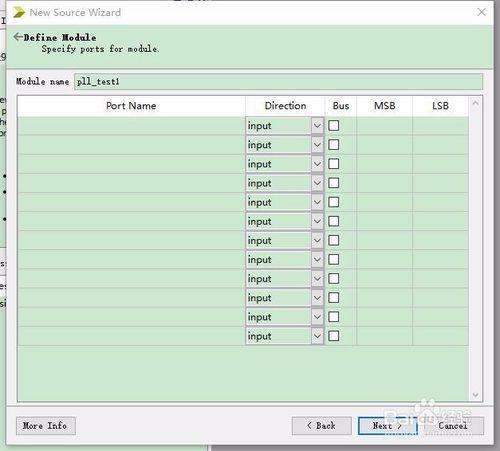

出現如下對話方塊,直接next。

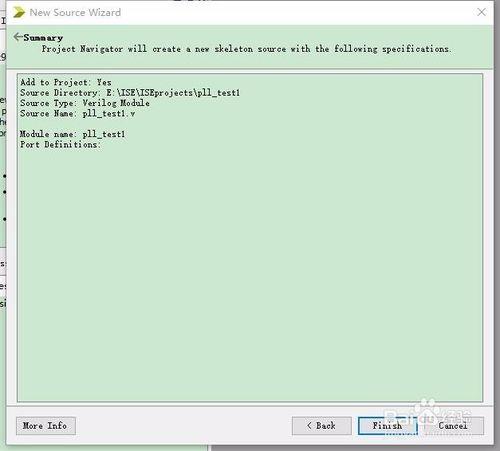

之後,出現如下對話方塊,也不用修改,直接點選finish。

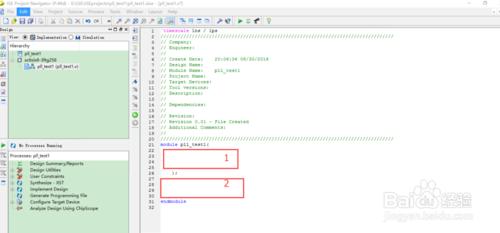

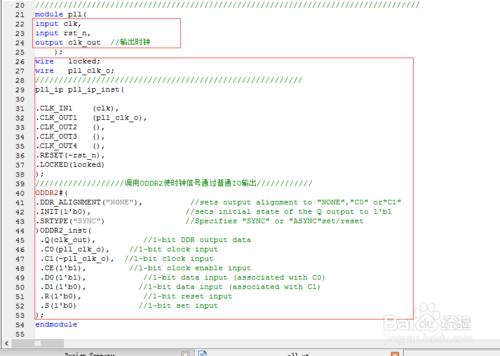

如下圖所示,可以開始編寫程式設定PLL了。在標紅1處填寫埠,2處寫描述語言。

如下圖所示,紅色方框內,為要填寫的內容。

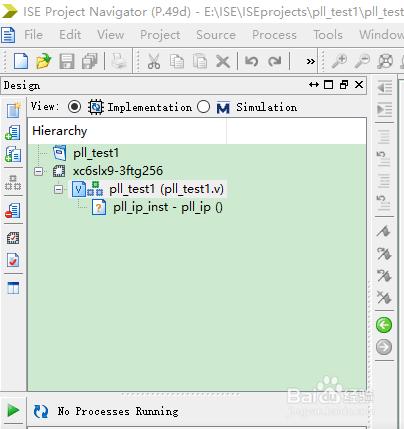

儲存後,左上角Hierarchy處,變成如下圖所示,滑鼠右擊pll_test1.v檔案。

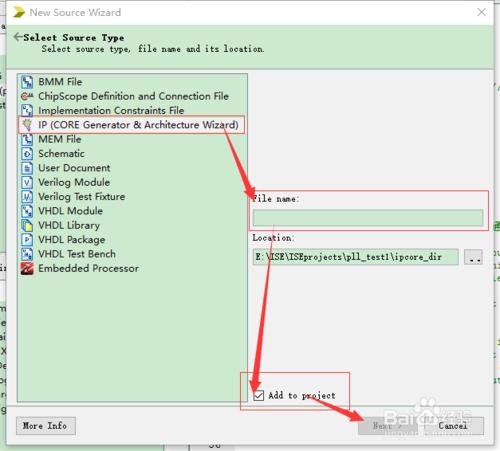

右擊pll_test1後,點選New source ,出現如下對話方塊,選擇

IP(CORE Generator&Architecture Wizard),起個名字(此處起名需注意要與程式中子模組名字一致,如本程式,為pll_ip),勾選上add to project ,點選next。

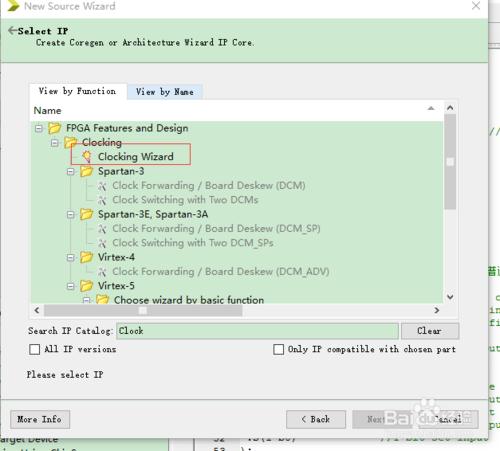

然後出現如下對話方塊,選擇Clocking Wizard ,點選next,再點選finish。

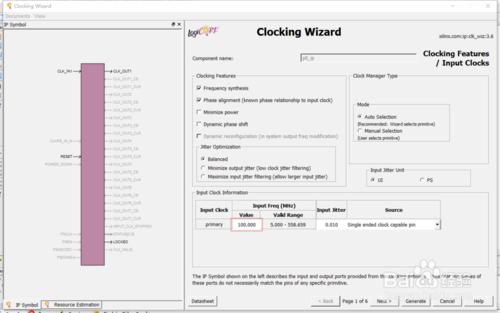

出現如下圖所示,在標紅的部分,修改為所輸入的時鐘(本例為50),別處不用修改,點選next。

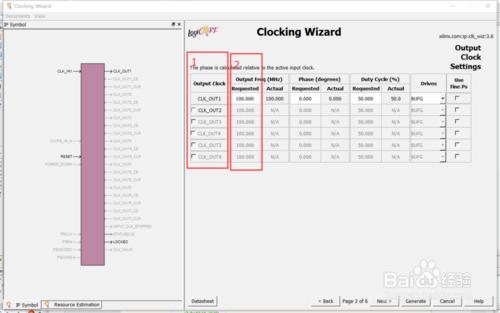

然後出現如下對話方塊,在紅框1中選擇要輸出的埠,紅框2中修改要輸出的值,然後點選next。

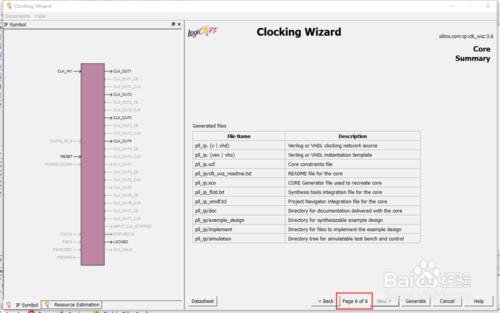

第三頁不用修改,直接點選next,第四頁與不用修改,直接點選next,第五頁也不用修改,直接點選next,第六頁也不用修改,點選generate.在下圖中標紅部分看頁數。

OK,到這時就已經完成工作啦,自己新增UCF檔案,下載到板子上試試吧。