quartus軟體內建了很多我們經常用到的電路模組,統稱為巨集模組,在做EDA設計的時候,我們可以直接呼叫他們來簡化設計過程。不要小看了巨集模組,如果利用得當,可以省去你一多半的設計時間呢。這裡以FIFO先進先出巨集模組為例,說明在quartus中怎樣新增巨集模組。

工具/原料

quartus II 9.0

步驟/方法

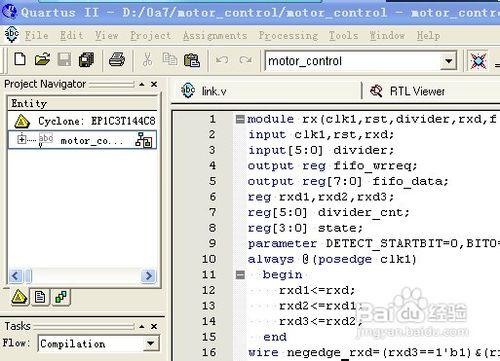

執行選單【File】-【Open Project…】命令,在quartus中開啟一個設計專案

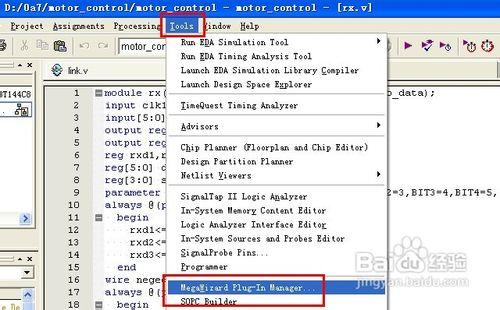

執行選單【Tools】-【Megawizard Plug-In Manager…】命令,開啟Megawizard Plug-In Manager設定嚮導

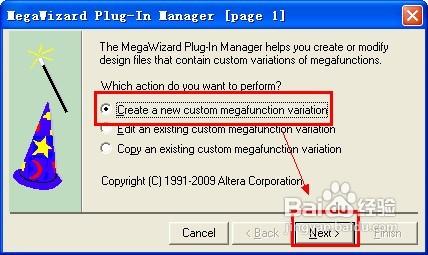

這裡我們是新增一個全新的巨集模組,所以選擇【Creat a new custom megafunction variation】,點選【next】按鈕

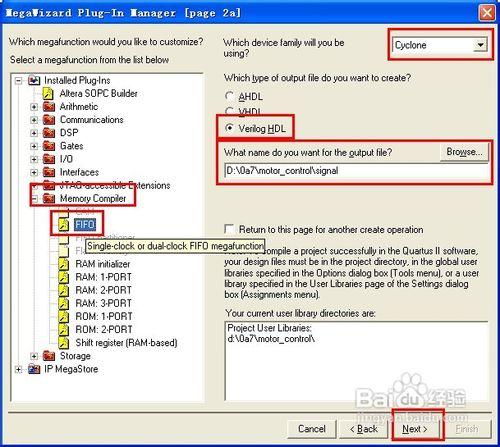

右上方會顯示你所用的晶片系列,在左側樹形列表裡選擇你需要的巨集模組,這裡選擇【Memory Compiler】-【FIFO】先進先出模組,選擇所要生成的語言和FIFO模組的儲存路徑及檔名,點選【next】按鈕

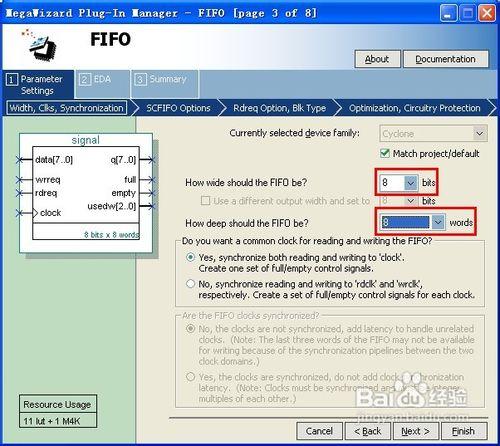

How wide should the FIFO be?後填寫你建立的FIFO位寬多少,How deep should the fifo be?後填寫你的FIFO深度,也就是能裝多少個數據,下一步【next】

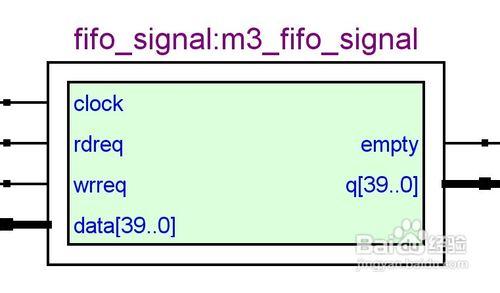

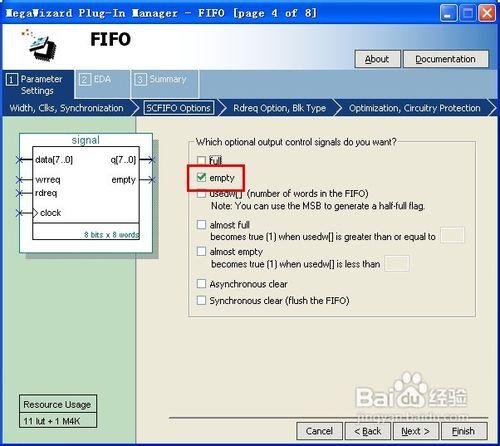

一般情況下,FIFO輸出我們只選擇資料q[#:0]和empty就可以了,所以去掉empty以為所有專案前的對勾,下一步【next】

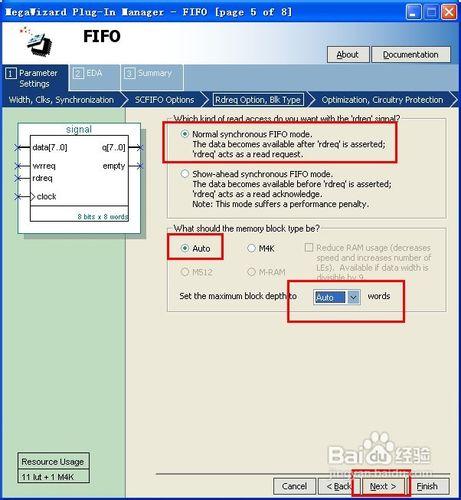

這一步可以預設設定不變,下一步【next】

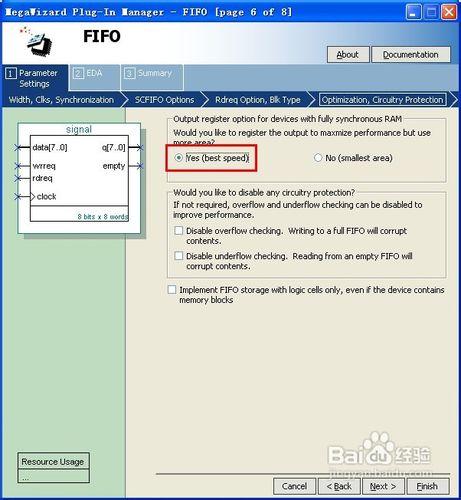

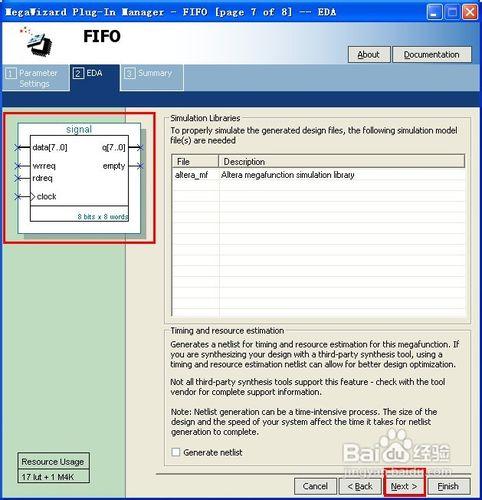

一般情況下在page 6 of 8 中選擇【Yes(best speed)】,下一步【next】,page7 of 8預設不變,下一步【next】

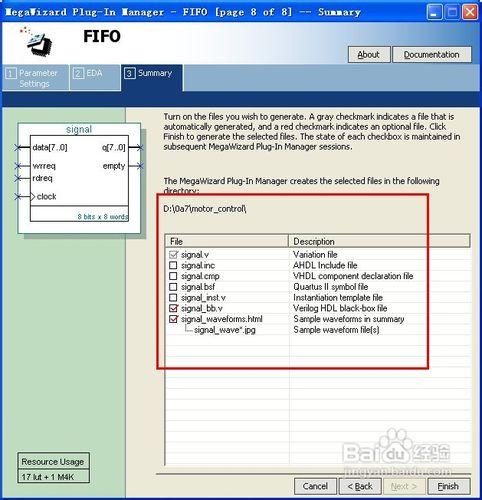

巨集模組嚮導最後一步,這裡會顯示嚮導生成的所有檔名,及其描述,一般情況下預設即可,點選【finis】儲存並退出嚮導

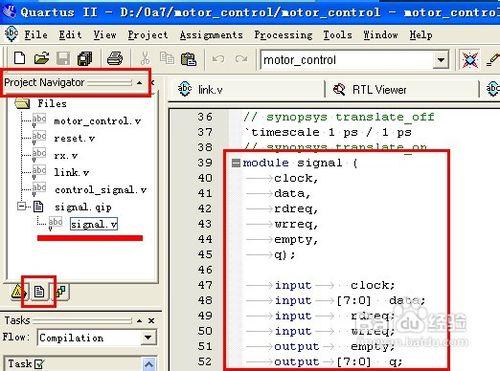

我們可以在軟體的【project Navigator】-【Files】中看到我們新新增的巨集模組檔案,因為在第4步我們選擇的是Verilog HDL,所以生成檔案是Verilog HDL程式碼編寫的。

注意事項

讀者可以依照此過程,新增其他巨集模組到自己的設計中